|

图(23) Step1: 给VDD上最高电压,并且tester的电压源设定一个钳制电流,防止电流过大损测试机。 Step2: 让芯片持续不断的运行特定的pattern,等待5~10ms。Step3: 量测流过VDD上的电流,根据datasheet中的标识设定limit,超过limit表示坏品。

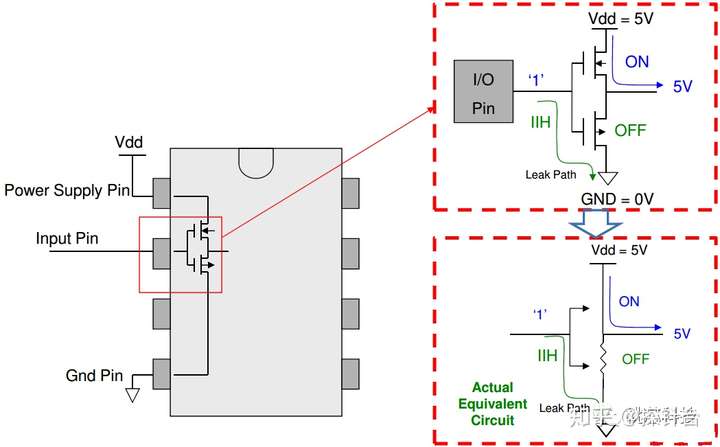

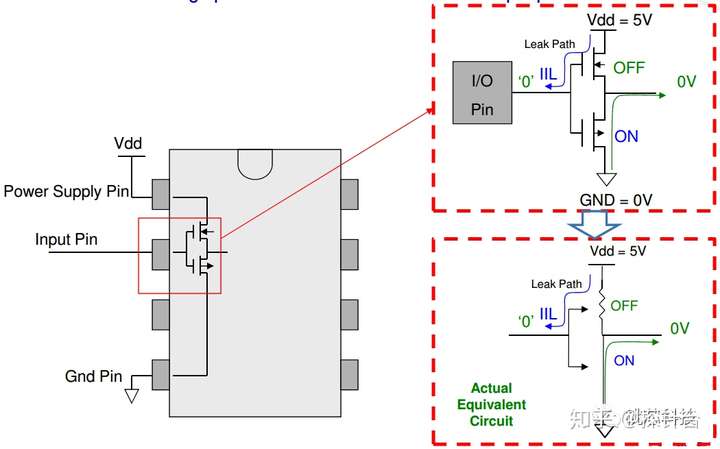

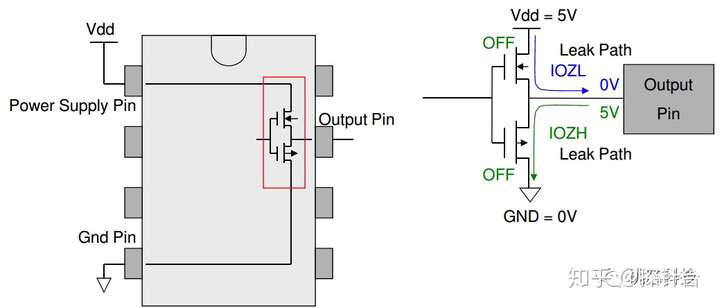

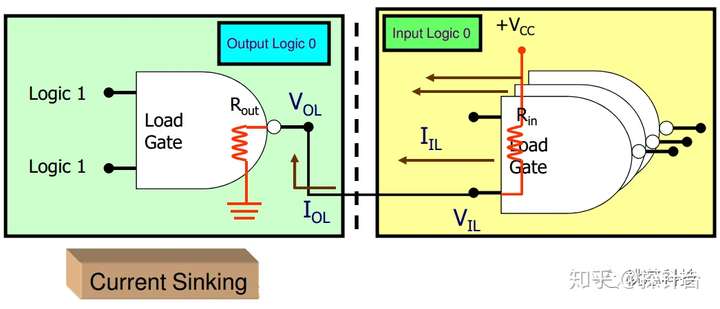

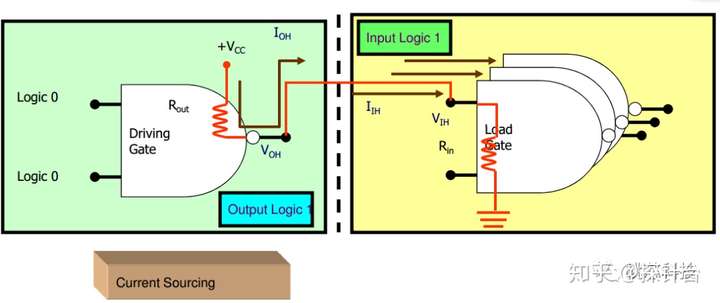

Leakage测试 芯片内部晶体管不可能在理想的状态,因此或多或少会存在一定的漏电流,需要测试漏电,保证漏电是在正常的允许的范围内,而不是潜在的defect。 Input Leakage Test(IIH and IIL) IIH是当芯片的某个input pin被设定为输入VIH时,从这个input pin到芯片的ground之间的漏电流,如下图(24)所示  图(24) IIL是当芯片的某个input pin被设定为输入VIL时,从芯片的VDD 到这个input pin的之间的漏电流,如下图(25)所示  图(25) Output Tristate Leakage Test(IOZL and IOZH) Tristate表示的是输出pin是高阻状态,当这个时候,如果输出pin上有电压VDD,那么从输出pin到芯片的ground上会有漏电(IOZH);如果输出pin接地,那么从芯片的VDD到这个输出pin上也会有漏电(IOZL),如下面图(26)所示,这些漏电必须保持在spec规定的范围内,以确保芯片的正常工作,不会有潜在的defect产生。  图(26) Output Logic Low DC Test(VOL/IOL) VOL表示的是当输出pin为状态low的时候的最大电压,IOL表示的是在此种状态下这个输出pin的最大的电流驱动能力,这个项目是测试当此状态下的输出pin对地的电阻大小,如下面图(27)所示。  图(27) Output Logic High DC Test(VOH/IOH) VOH表示的是当输出pin为状态high的时候的最小电压,IOH表示的是在此种状态下这个输出pin的最大的电流驱动能力,这个项目是测试当此状态下的芯片的VDD到这个输出pin的电阻大小,如下面图(28)所示。  图(28) 随着芯片工艺越来越先进,晶体管密度越来越高,芯片测试的复杂度和难度也成倍地增长。本文通过各种失效模式及检测机理的讨论,梳理了一下基本的测试概念。后续我们会再针对混合信号测试、RF测试、DFT测试进行一些探讨,谢谢!

芯片测试科普第三章 |  楼主|

发表于 2020-3-17 10:08

楼主|

发表于 2020-3-17 10:08

楼主|

发表于 2020-3-17 10:08

楼主|

发表于 2020-3-17 10:08